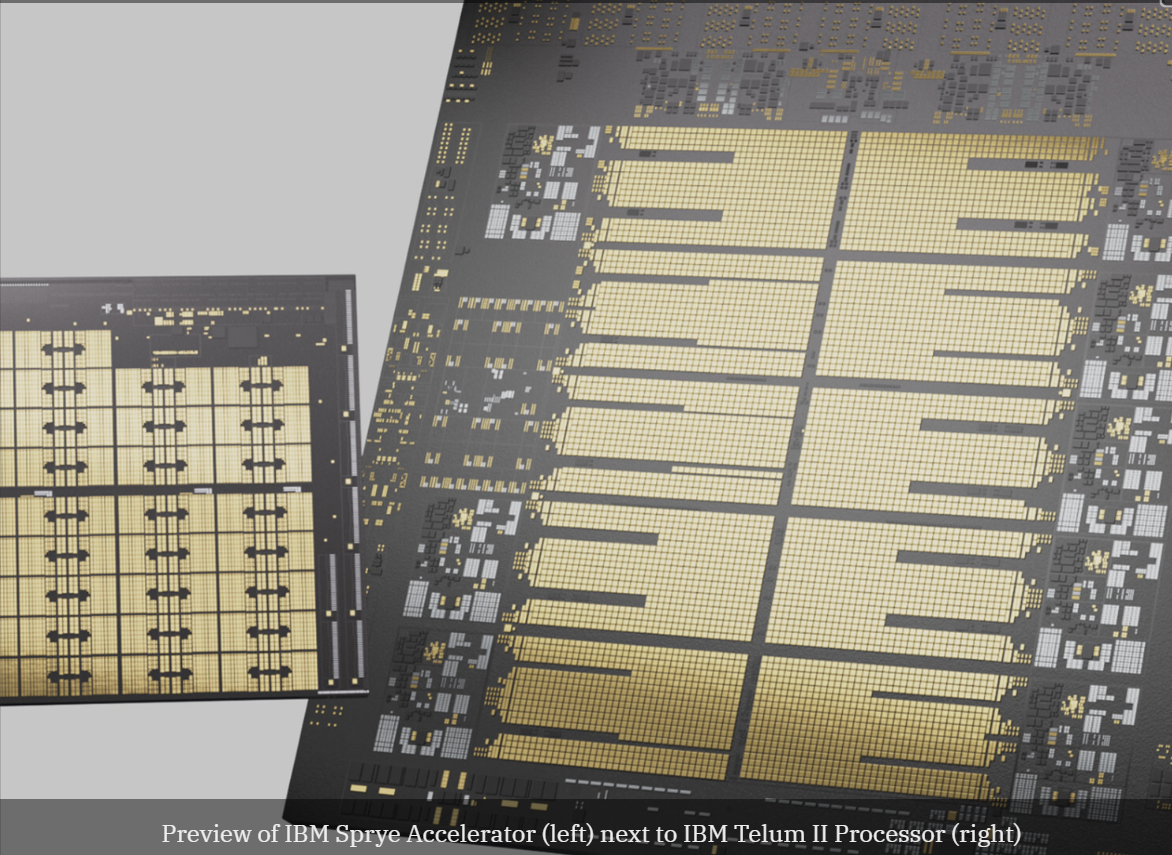

IBM is looking to give its IBM Z systems an AI and large language model (LLM) twist as it outlined its upcoming IBM Telum II Processor and IBM Spyre Accelerator for upcoming mainframes.

At the Hot Chips 2024 conference, IBM is outlining new processors and architectures to keep mainframes relevant in an AI age.

IBM outlined the following at Hot Chips to service AI workloads on mainframes:

- IBM Telum II processor, which will power the next-gen IBM Z systems. The new IM chip has more memory capacity, 40% growth in cache and an integrated AI accelerator core connected to a Data Processing Unit (DPU) compared to the first generation Telum.

- Telum II features eight cores running at 5.5GHz, with 36MB L2 cache per core and a 40% increase in on-chip cache capacity for a total of 360MB.

- The new DPU on Telum II is designed to accelerate IO for networking and storage.

- IBM Spyre Accelerator, which will complement Telum II and provide more AI compute. IBM said Telum II and Spyre are designed for ensemble methods of AI modeling that combine multiple models with encoder LLMs. Spyre will be an add-on option for IBM Z systems and features up to 1TB of memory.

- The chips will be manufactured by Samsung Foundry on a 5nm process node.

- Use cases include for these chips for IBM's next-gen mainframes include insurance claim fraud detection, anti-money laundering and AI assistants.

According to IBM, Telum II will be the CPU for the next-gen IBM Z and IBM LinuxOne with availability in 2025. IBM Spyre Accelerator is in tech preview with availability in 2025.

Related: